#### République Algérienne Démocratique et Populaire Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

## Université de Batna Faculté des Sciences

#### **Thèse**

En vue de l'obtention du diplôme de

#### Doctorat en Sciences en Informatique

## Architecture Parallèle pour l'accélération de la recherche dans les routeurs IP

Présentée Par

#### **Hichem HOUASSI**

Soutenue le 06/06/2012

#### Devant le jury composé de :

Directeur de thèse Pr. BILAMI Azeddine

Président Pr. BOUGUECHAL Nouredine Professeur UHL Batna

Examinateurs Pr. BENMOHAMMED Mohamed Professeur UMC Constantine

Pr. CHAOUI Allaoua Professeur UMC Constantine

Professeur UHL Batna

Dr. BELATTAR Brahim M.C.A UHL Batna

#### REMERCIEMENTS

#### Grand merci à Dieu.

Cette thèse représente un travail mené pendant plusieurs années. Il serait très difficilement réalisable sans le soutien et l'accompagnement de l'entourage. C'est pourquoi Je tiens à remercier toutes les personnes qui m'ont aidé durant ces années de thèse.

Je remercie plus particulièrement Monsieur BILAMI Azeddine, Professeur à l'Université Hadj Lakhdar Batna, pour m'avoir encadré. Je le remercie pour sa pédagogie, son soutien et pour toutes les discussions instructives et fructueuses menées durant toute la durée de ce travail de recherche.

Je remercie vivement Monsieur BOUGUECHAL Noureddine, Professeur à l'Université Hadj Lakhdar Batna, pour avoir accepté de présider le jury de cette thèse.

Mes remerciements sont aussi pour Messieurs BENMOHAMMED Mohamed, Professeur à l'Université Mentouri Constantine, CHAOUI Allaoua, Professeur à l'Université Mentouri Constantine, et BELATTAR Brahim Maitre de conférences à l'Université Hadj Lakhdar Batna, pour l'intérêt qu'ils portent à ces travaux, et en acceptant de faire partie du jury de cette thèse.

Je remercie vivement ma famille de m'avoir laissé travailler durant autant d'années sans (trop) poser de questions et de m'avoir fait confiance.

Enfin, je souhaite remercier ma femme, pour son soutien et sa compréhension, qui m'ont permis de venir à bout de mes objectifs.

### Résumé

Le réseau Internet est composé de nœuds et de routeurs reliés ensemble par des médias de transmission (liens). Les paquets de données transitent sur les liens, d'un routeur à un autre, vers leurs destinations finales. Chaque routeur exécute une décision d'expédition sur les paquets entrants pour déterminer le prochain routeur du paquet.

Le routeur Internet est un dispositif permettant de choisir le chemin que les paquets de données vont emprunter pour arriver à leurs destinations. Pour ce faire, le routeur effectue une recherche dans la table de routage en utilisant l'adresse de destination d'un paquet IP comme une clé; cette tâche du routeur est appelée décision de routage. La croissance du nombre d'utilisateurs d'Internet à comme conséquence l'augmentation des tailles des tables de routage des routeurs et la complexité de l'opération d'expédition des paquets de données.

La décision de routage consiste à chercher la meilleure route pour un paquet à partir de son adresse IP destination. Afin d'augmenter l'efficacité du routage dans l'Internet, plusieurs adresses destination sont agrégées en une seule entrée dans une table de routage (préfixe). Depuis l'avènement du CIDR (*Classless Inter-Domain Routing*), les préfixes dans la table de routage ont des longueurs variables, alors plusieurs préfixes peuvent être associés à une même adresse IP de destination, le routeur doit choisir le plus long préfixe correspondant (PLP) à l'adresse IP. Etant donné que les préfixes dans la table de routage ont des longueurs différentes, alors, nous ne pouvons pas trouver la correspondance en utilisant un algorithme de recherche avec une correspondance exacte. Par conséquent, les performances du routeur dépendent fortement de l'efficacité de l'opération de recherche du plus long préfixe dans la table de routage.

Différentes approches logicielles et matérielles ont été proposées et déployées pour améliorer les performances des routeurs, et dont la métrique de performance a été principalement le débit ou le nombre de paquets expédiés par seconde. Dans cette thèse nous avons proposé trois mécanismes de recherche du plus long préfixe correspondant à une adresse IP dans une table de routage, les mécanismes que nous avons proposés dans cette thèse contribuent à améliorer la performance de l'acheminement de paquets dans les routeurs IP.

#### Mots clés:

Routeur IP, Table de routage, plus long préfixe, architecture parallèle, description VHDL, algorithme parallèle, expansion des préfixes, table de routage cache, arbre binaire, arbre binaire à contenu dynamique.

### **Abstract**

The Internet network is composed of nodes and routers connected by transmission media (links). The data packets pass on links via routers until reaching their final destinations. Every router performs a packet forwarding decision on the incoming packet in order to determine the next-hop router. To do this, the router searches the routing table using the destination IP address of an IP packet as a key; this task is called the routing decision. The growing number of Internet users lead to the growing of the routing table sizes and the increasing of the complexity of the forwarding data packet operation.

Considering some criterion, the routing decision chooses the best route for a packet for its destination IP address. To increase the efficiency of routing in the Internet, several destination addresses are aggregated into a single entry in a routing table (prefix). Since the advent of CIDR (Classless Inter-Domain Routing), prefixes in the routing table became with variable lengths, so that multiple prefixes may be associated with the same destination IP address, the router must choose the longest matching prefix (LMP) to the IP address. Since the prefixes in the routing table have different lengths, we cannot find a matching algorithm using an exact match search. Therefore, router performance depends heavily on the effectiveness of the longest prefix search operation in the routing table.

Different hardware and software approaches have been proposed and deployed to improve the performance of routers, primarily evaluated in terms of the number of packets forwarded per second. In this thesis we propose three mechanisms of the IP address search operation in a routing table. The proposed mechanisms contribute to improve the performance of packet forwarding in IP routers.

#### **Key words:**

IP Router, Routing table, longest prefix, parallel architecture, VHDL description, parallel algorithm, Prefix expansion, Cache routing table, IP address lookup, binary trie, dynamic content binary trie.

## Table des matières

| LISTE DES FIGURES                                                        | IX  |

|--------------------------------------------------------------------------|-----|

| LISTE DES TABLEAUX                                                       | XI  |

| LISTE DES ABREVIATIONS                                                   | XII |

| Chapitre 1 : Introduction                                                |     |

| 1.1. Introduction                                                        | 1   |

| 1.2. Protocole IP et adressage                                           | 2   |

| 1.2.1. Protocole IP                                                      | 2   |

| 1.2.2. Evolution d'adressage IP                                          | 3   |

| 1.2.2.1. L'adressage avec classes                                        | 3   |

| 1.2.2.1.1. Structure de l'adresse IP                                     | 3   |

| 1.2.2.1.2. Classes d'adresses IP                                         | 4   |

| 1.2.2.1.3. Adresses IPv4                                                 | 5   |

| 1.2.2.1.4. Adresses IPv6                                                 | 5   |

| 1.2.2.1.5. Sous-réseaux                                                  | 6   |

| 1.2.2.2. Structuration des adresses et agrégation                        | 6   |

| 1.2.2.2.1. Evolution des tailles des tables de routage                   | 7   |

| 1.2.2.2.2. CIDR (Classless Inter-Domain Routing)                         | 7   |

| 1.3. Recherche d'information de routage dans un routeur IP               | 10  |

| 1.3.1. Routeurs IP                                                       | 10  |

| 1.3.2. Table de routage                                                  | 11  |

| 1.3.3. Consultation d'adresses IP (Notre contribution)                   | 12  |

| 1.3.3.1. Consultation d'adresses IP dans le cas d'adressage en classes   | 12  |

| 1.3.3.2. Consultation d'adresses IP dans le cas d'adressage sans-classes | 13  |

| 1.4. Difficulté de recherche des informations de routage                 | 14  |

| 1.5. Contributions                                                       | 15  |

| 1.6. Plan de la thèse                                                    | 17  |

| 1.7. Conclusion                                                          | 17  |

#### **Chapitre 2 : Travaux dans le domaine**

| 2.1. Introduction                                                                                                     | 19       |

|-----------------------------------------------------------------------------------------------------------------------|----------|

| 2.2. Solutions logicielles et structures de données utilisées                                                         | 20       |

| 2.2.1. Recherche linéaire                                                                                             | 20       |

| 2.2.1.1. Recherche linéaire basée sur les longueurs en utilisant les tables de hachage                                | 20<br>20 |

| 2.2.2.1. Algorithmes de recherche binaires basés sur les bits des préfixes                                            | 20       |

| 2.2.2.2. Algorithmes de recherche binaires basés sur les points d'extrémités des plages d'adresses IP (Ranges search) | 29<br>32 |

| 2.3. Solutions matérielles                                                                                            | 39       |

| 2.3.1. Mémoire adressable par contenu CAMs et Ternary CAMs                                                            | 39       |

| 2.3.1.1. Utilisation des CAMs et TCAMs dans les routeurs Internet                                                     | 40       |

| 2.3.1.2. Architecture des CAMs / TCAMs                                                                                | 41       |

| 2.3.1.3. Recherche dans les CAMs / TCAMs                                                                              | 42       |

| 2.3.1.4. Architectures des CAMs / TCAMs proposées pour l'opération de lookup                                          | 43<br>44 |

| 2.3.3. Architectures multiprocesseurs                                                                                 | 46       |

| 2.3.3.1. Manipulation des tables de routage en parallèle                                                              | 47       |

| 3.4. Conclusion                                                                                                       | 48       |

| Chapitre 3 : Parallélisme et architectures parallèles                                                                 |          |

| 3.1. Introduction                                                                                                     | 49       |

| 3.2. Origine du parallélisme                                                                                          | 49       |

| 3.3. Sources de parallélisme                                                                                          | 50       |

| 3.4. Limites du parallélisme                                                                                          | 51       |

| 3.5. Architectures parallèles                                                                                         | 52       |

| 3.5.1. Classifications des architectures parallèles                                                                   | 53       |

| 3.5.1.1. Classification de Flynn                                                                                      | 53       |

| 3.5.1.1.1. Architecture SISD (Single Instruction stream, Single Data stream)                                          | 53       |

| 3.5.1.1.2. Architecture SIMD (Single Instruction stream, Multiple Data stream)                                        | 54       |

#### TABLE DES MATIERES

| 3.5.1.1.3. Architecture MISD (Multiple Instruction stream, Single Data stream)         | 56 |

|----------------------------------------------------------------------------------------|----|

| 3.5.1.1.4. Architecture MIMD (Multiple Instructions stream, Multiple Data              |    |

| stream)                                                                                | 57 |

| 3.5.1.2. Classification de Duncan                                                      | 58 |

| 3.5.2.1. Architectures synchrones                                                      | 58 |

| 3.5.2.2. Architectures asynchrones                                                     | 58 |

| 3.5.2.3. Architectures mixtes                                                          | 58 |

| 3.6. Modèles de programmation parallèle                                                | 59 |

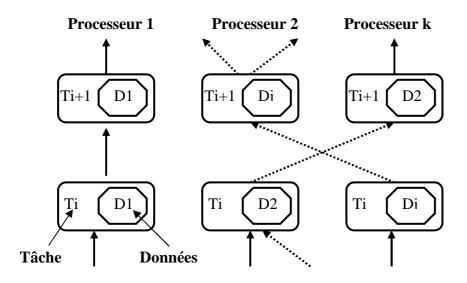

| 3.6.1. Parallélisme de données                                                         | 59 |

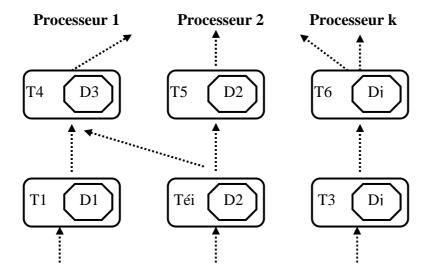

| 3.6.2. Parallélisme de contrôle                                                        | 60 |

| 3.7. Etapes de développement d'une application exécutée sur une architecture parallèle | 61 |

| 3.8. Conclusion                                                                        | 63 |

|                                                                                        |    |

| Chapitre 4 : L'architecture parallèle « PARIR »                                        |    |

| 4.1. Introduction                                                                      | 64 |

| 4.2. Conception assisté par ordinateur                                                 | 65 |

| 4.3. Modèles                                                                           | 66 |

| 4.4. Synthèse et Simulation                                                            | 66 |

| 4.4.1. Validation et vérification de description HDL                                   | 67 |

| 4.4.1.1. Simulation fonctionnelle                                                      | 67 |

| 4.4.2. Synthèse                                                                        | 68 |

| 4.5. Langages de description de matériel                                               | 69 |

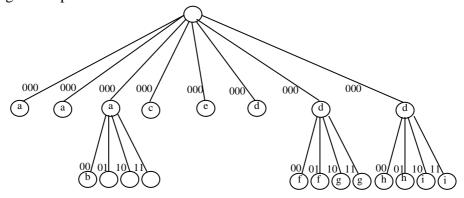

| 4.6. Parallélisation des données par la décomposition de la table de routage           | 69 |

| 4.6.1. Terminologie et définitions                                                     | 70 |

| 4.6.2. Algorithme de décomposition de la table de routage                              | 70 |

| 4.6.3. Procédure d'expansion des préfixes                                              | 70 |

| 4.6.4. Analyse des résultats                                                           |    |

| 4.7. Structure de données et algorithme parallèle                                      | 72 |

|                                                                                        | 74 |

| 4.7.1. Structure de données                                                            | 74 |

| 4.7.2. Algorithme parallèle                                                            | 74 |

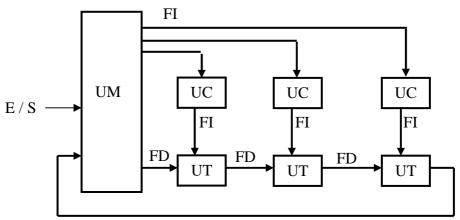

| 4.8. L'architecture parallèle « PARIR »                                                | 77 |

| 4.8.1. Description de l'architecture « PARIR »                                         | 77 |

#### TABLE DES MATIERES

| 4.8.2. Experimentations et resultats                                                                                                                                                             | 79         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.9. Modélisation de notre système                                                                                                                                                               | 81         |

| 4.9.1. Décomposition du système en modules                                                                                                                                                       | 81         |

| 4.9.2. Le langage VHDL                                                                                                                                                                           | 82         |

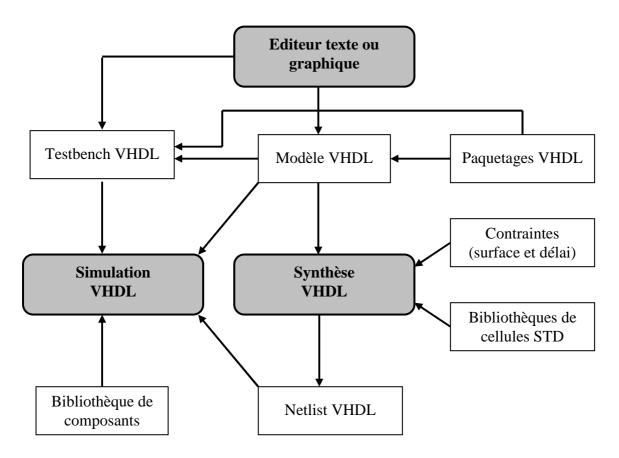

| 4.9.2.1. Flot de conception basé sur le VHDL                                                                                                                                                     | 83         |

| 4.9.2.2. Organisation d'un modèle VHDL                                                                                                                                                           | 84         |

| 4.9.2.2.1. Unités de conception                                                                                                                                                                  | 84         |

| 4.9.2.2.2. Entité de conception                                                                                                                                                                  | 84         |

| 4.9.3. Modélisation et simulations des modules de notre système                                                                                                                                  | 85         |

| 4.9.3.1. Le sélecteur                                                                                                                                                                            | 85         |

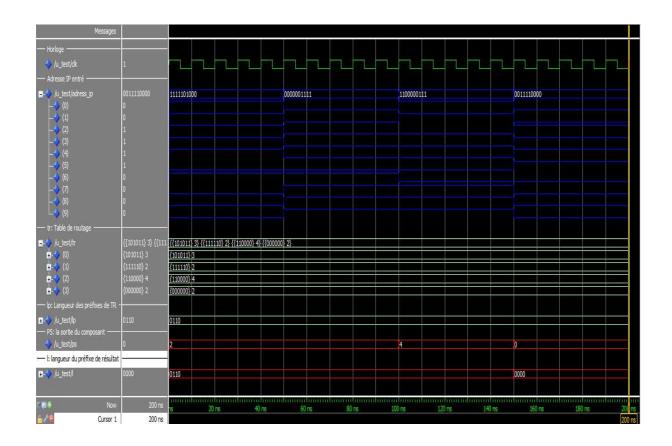

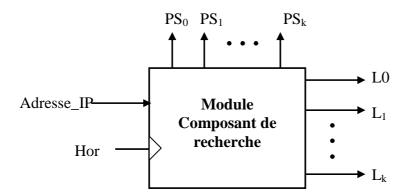

| 4.9.3.2. Le composant de recherche                                                                                                                                                               | 89         |

| 4.9.3.3. Le système complet                                                                                                                                                                      | 93         |

| 4.10. Conclusion                                                                                                                                                                                 | 94         |

| Chapitre 5 : Solutions logicielles proposées  5.1. Introduction                                                                                                                                  | 96         |

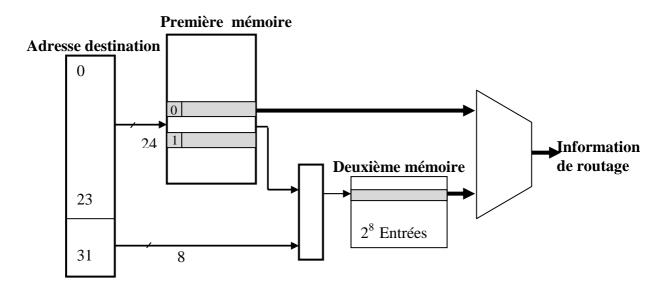

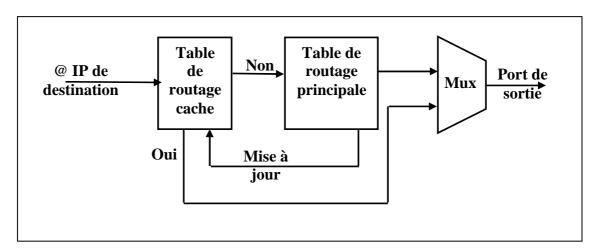

| 5.2. Routeur avec une table de routage cache                                                                                                                                                     | 96         |

| 5.2.1. Structure de la table de routage                                                                                                                                                          | 90         |

| 5.2.1.1. Table de routage principale                                                                                                                                                             | 97         |

| 5.2.1.2. Table de routage cache                                                                                                                                                                  | 98         |

| <ul> <li>5.2.2. Algorithme de remplacement des entrés de la table cache (la moins récemment utilisée)</li> <li>5.2.3. Ordonnancement de la table cache</li> </ul>                                | 99<br>100  |

| 5.2.4. Expérimentation                                                                                                                                                                           | 100        |

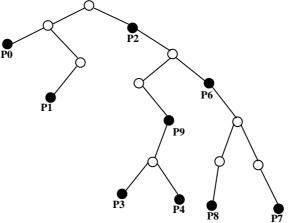

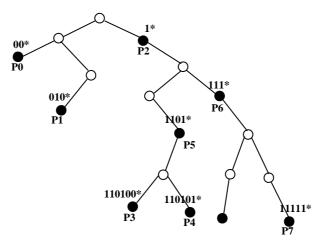

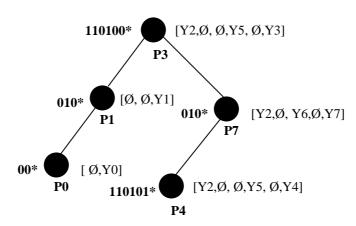

| <ul><li>5.3. Algorithme de recherche des informations de routage par arbre binaire à contenu dynamique (ABCD)</li><li>5.3.1. Description de l'arbre binaire à contenu dynamique (ABCD)</li></ul> | 102<br>103 |

| 5.3.1.1. Structure des nœuds de l'arbre ABCD                                                                                                                                                     | 104        |

| 5.3.1.2. Construction de l'arbre ABCD                                                                                                                                                            | 105        |

| 5.3.2. Algorithme de recherche du plus long préfixe correspondant dans l'arbre ABCD                                                                                                              | 106        |

| 5.3.3. Expérimentation et résultats                                                                                                                                                              | 107        |

| 5.4 Conclusion                                                                                                                                                                                   | 100        |

#### TABLE DES MATIERES

| Chapitre 6 : Conclusion et perspectives |     |

|-----------------------------------------|-----|

| Bibliographie                           | 112 |

## Liste des figures

| Figure.1.1.                                                                                | Classes d'adresses IP                                                                                              |    |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----|

| Figure.1.2.                                                                                | Evolution de la taille des tables de routage [8]                                                                   | 7  |

| Figure.1.3.                                                                                | Architecture d'un routeur Internet                                                                                 |    |

| Figure.1.4. Implémentation de l'opération de <i>lookup</i> dans le cas d'adressage classes |                                                                                                                    | 12 |

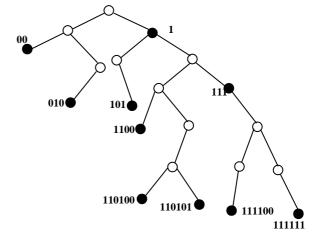

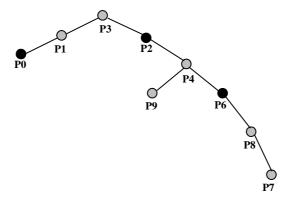

| Figure.2.1.                                                                                | Arbre binaire construit à partir du tableau                                                                        | 21 |

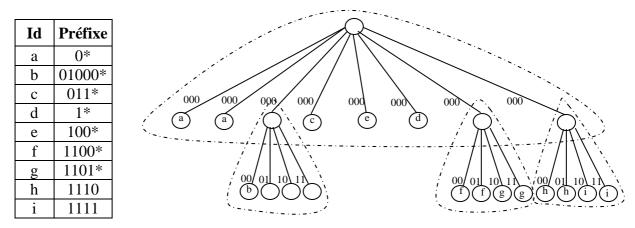

| Figure.2.2.                                                                                | Trie multibit à pas fixe                                                                                           | 22 |

| Figure.2.3.                                                                                | Trie multibit à préfixes disjoints                                                                                 | 22 |

| Figure.2.4.                                                                                | Schéma de Gupta et al (Implémentation matérielle de l'arbre multibit)                                              | 23 |

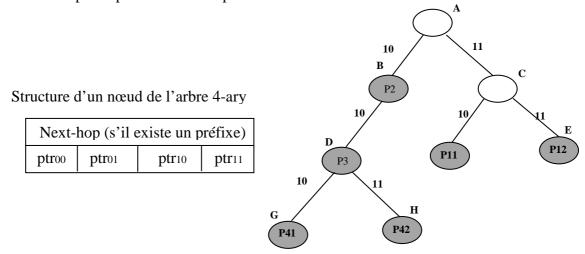

| Figure.2.5.                                                                                | Un arbre 4-ary stockant les préfixes du tableau 2.2. Les nœuds gris stockant des pointeurs vers le <i>Next-hop</i> | 24 |

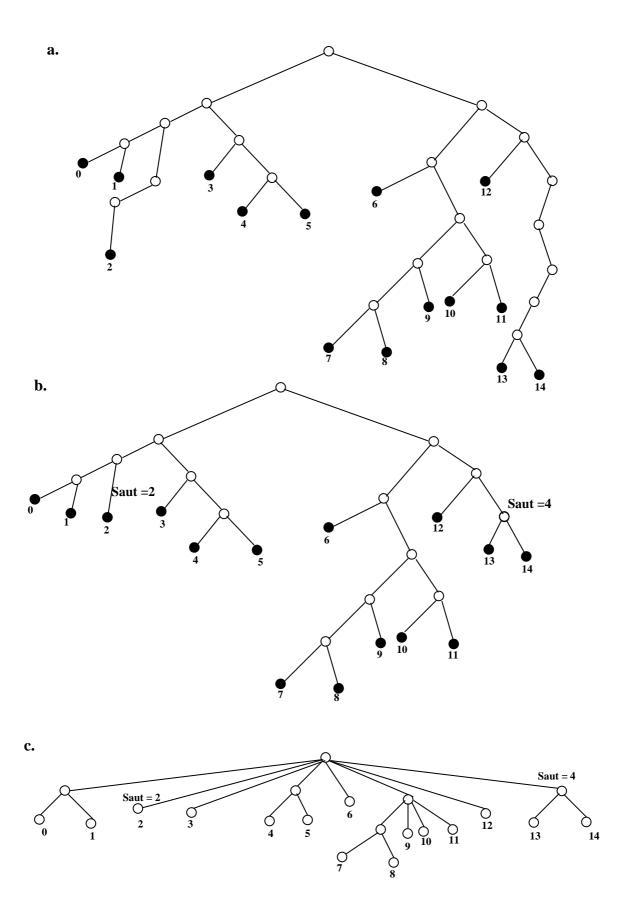

| Figure.2.6.                                                                                | a. arbre binaire ; b. arbre à chemins compressés (PC-Trie) ; c. arbre à niveaux compressés (LC-Trie)               | 26 |

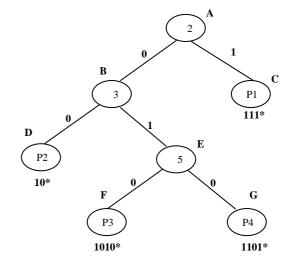

| Figure.2.7.                                                                                | Le Trie PATRICIA pour l'exemple du tableau.3.4                                                                     | 27 |

| Figure.2.8.                                                                                | Arbre binaire classique                                                                                            | 28 |

| Figure.2.9.                                                                                | Arbre de priorité                                                                                                  | 28 |

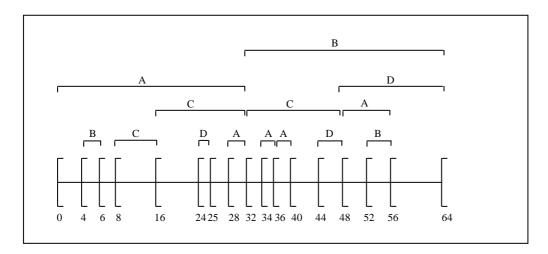

| Figure.2.10.                                                                               | Les plages représentent les préfixes du tableau3.5                                                                 | 30 |

| Figure.2.11.                                                                               | Arbre binaire équilibré pour l'exemple du tableau.3.8                                                              | 34 |

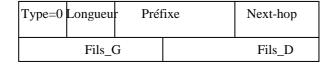

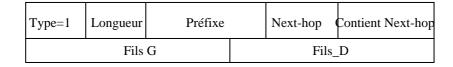

| Figure.2.12.                                                                               | Structure d'un nœud de l'arbre LPFST [38]                                                                          | 35 |

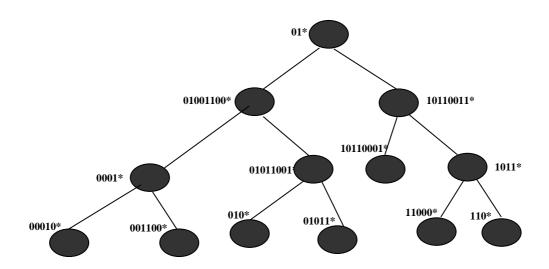

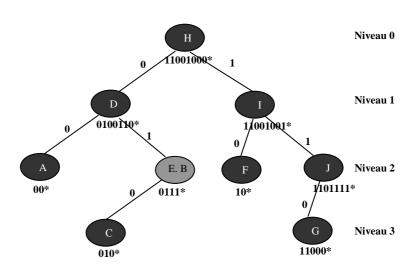

| Figure.2.13.                                                                               | Le Trie LPFST pour l'exemple du tableau3.9                                                                         | 36 |

| Figure.2.14.                                                                               | Algorithme de recherche du plus long préfixe dans l'arbre LPFST [38]                                               | 36 |

| Figure.2.15.                                                                               | Exemple d'un arbre binaire classique                                                                               | 37 |

| Figure.2.16.                                                                               | L'arbre binaire avec vecteur équivalent à l'arbre de la figure.3.15                                                | 38 |

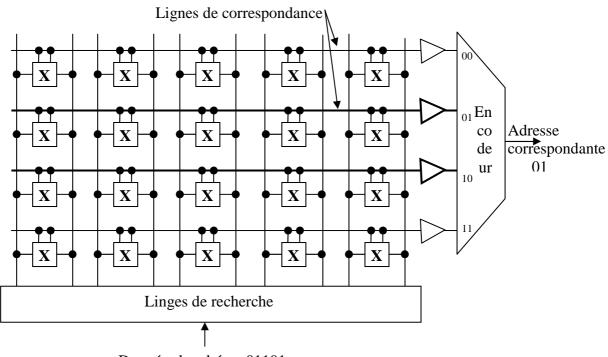

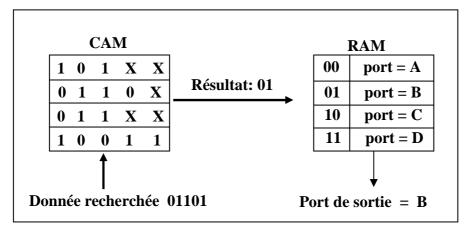

| Figure.2.17.                                                                               | Architecture du TCAM [72]                                                                                          | 42 |

| Figure.2.18.                                                                               | Architecture du CAM /RAM [72]                                                                                      | 42 |

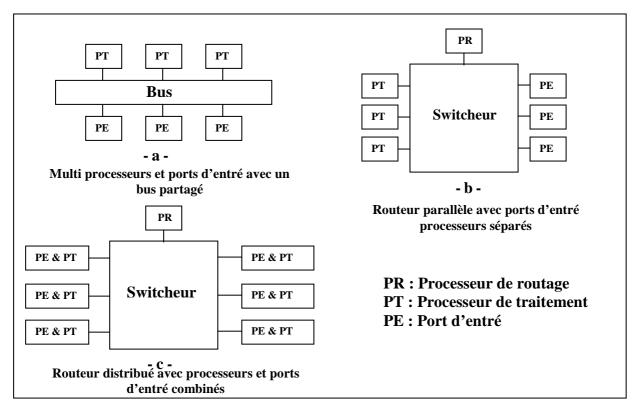

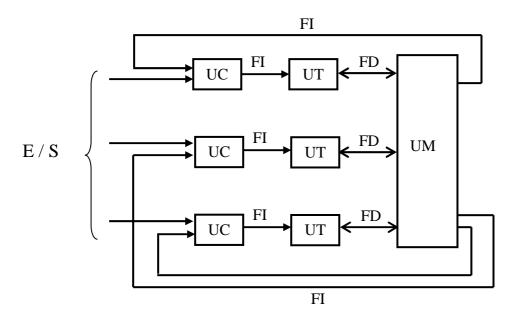

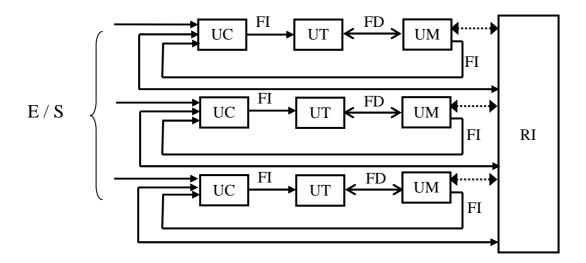

| Figure.2.19.                                                                               | Architectures des routeurs                                                                                         | 47 |

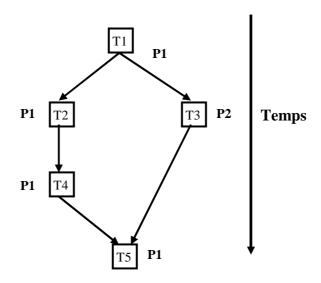

| Figure.3.1.                                                                                | Parallélisme de données                                                                                            | 50 |

| Figure.3.2.                                                                                | gure.3.2. Parallélisme de contrôle                                                                                 |    |

| Figure.3.3.                                                                                | re.3.3. Architecture SISD                                                                                          |    |

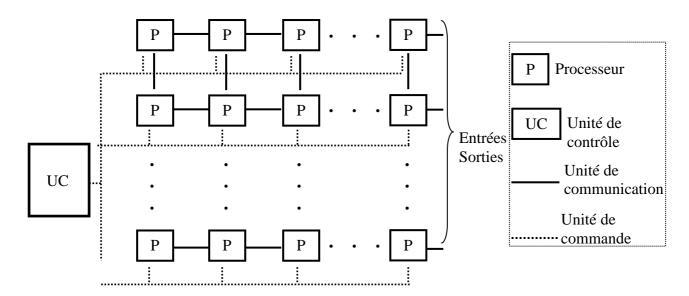

| Figure.3.4.                                                                                | Modèle de fonctionnement des architectures SIMD                                                                    | 55 |

| Figure.3.5.                                                                                | Architecture MISD.                                                                                                 | 56 |

| Figure.3.6.                                                                                | Architecture MIMD à mémoire partagée                                                                               | 57 |

#### LISTE DES FIGURES

| Figure.3.7.  | Architecture MIMD à mémoire distribuée                                               |     |  |

|--------------|--------------------------------------------------------------------------------------|-----|--|

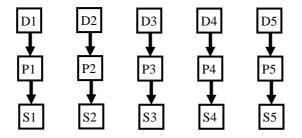

| Figure.3.8.  | 3. Parallélisme de données                                                           |     |  |

| Figure.3.9.  | Parallélisme de contrôle                                                             | 61  |  |

|              |                                                                                      |     |  |

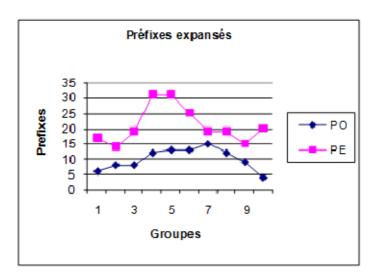

| Figure.4.1.  | Comparaison entre les préfixes expansés et originaux des 10                          |     |  |

|              | groupes des préfixes                                                                 | 73  |  |

| Figure.4.2.  | Comparaison entre les préfixes expansés et originaux en fonction du nombre de groupe | 73  |  |

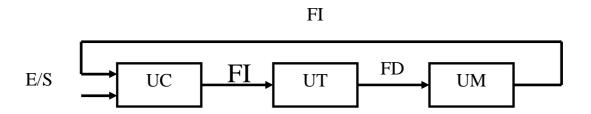

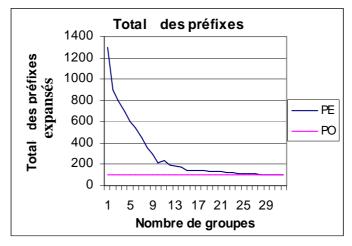

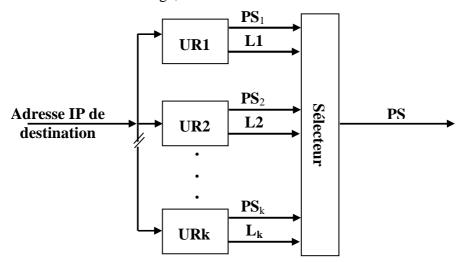

| Figure.4. 3. | Architecture de base                                                                 | 77  |  |

| Figure.4. 4. | Unité de recherche (UR)                                                              | 78  |  |

| Figure.4.5.  | Sélecteur                                                                            | 78  |  |

| Figure.4.6.  | Comparateur J                                                                        | 79  |  |

| Figure.4.7.  | Digramme des résultats obtenus                                                       | 80  |  |

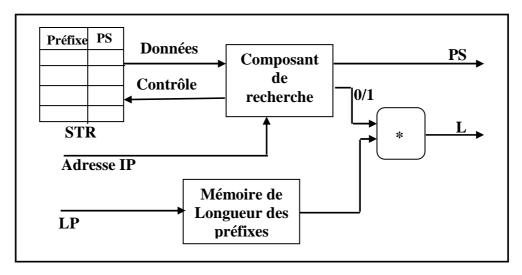

| Figure.4.8.  | Structure en module de notre système                                                 | 82  |  |

| Figure.4.9.  | Flot de conception basé sur VHDL [95]                                                | 84  |  |

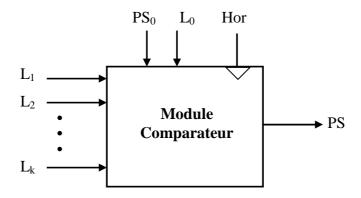

| Figure.4.10. | Vue externe d'un comparateur                                                         | 86  |  |

| Figure.4.11. |                                                                                      |     |  |

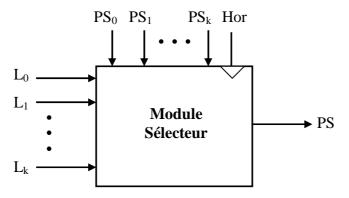

| Figure.4.12. | Vue externe d'un sélecteur                                                           | 87  |  |

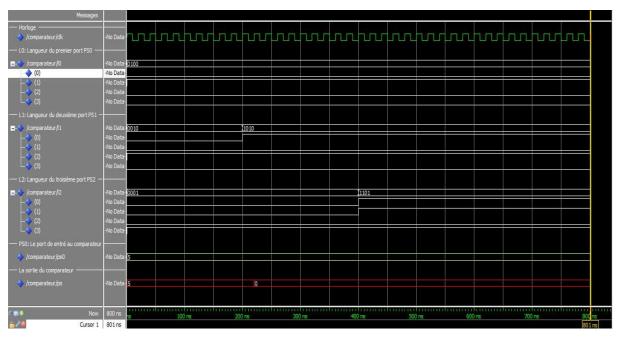

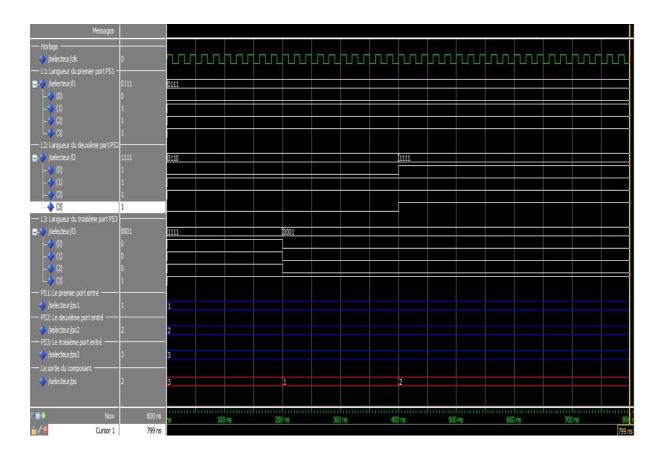

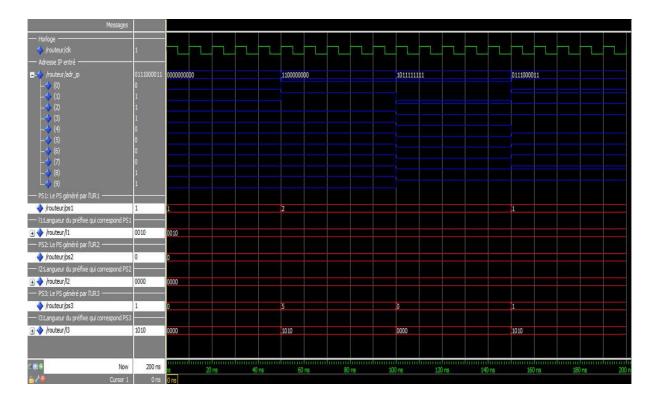

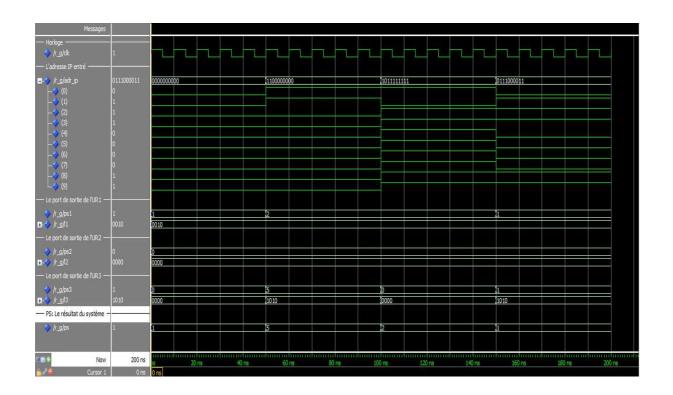

| Figure.4.13. | Résultat de simulation du module « sélecteur »                                       | 88  |  |

| Figure.4.14. |                                                                                      |     |  |

| Figure.4.15. | Résultat de simulation du module « Unité de Recherche »                              | 90  |  |

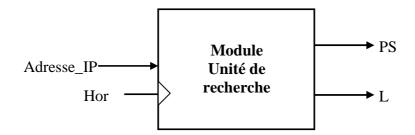

| Figure.4.16. | Vue externe d'un composant de recherche                                              | 91  |  |

| Figure.4.17. | Résultat de simulation du module « composant de recherche »                          | 92  |  |

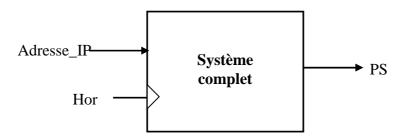

| Figure.4.18. | Vue externe du système complet                                                       | 93  |  |

| Figure.4.19. | Résultat de simulation du système complet                                            | 94  |  |

| Figure.5.1.  | Schéma d'un routeur avec une table de routage cache                                  | 97  |  |

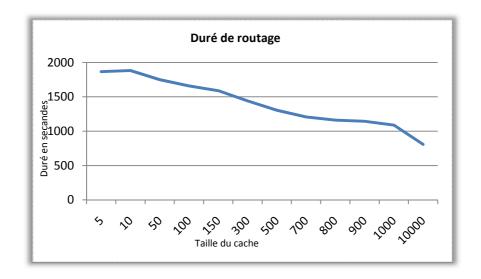

| Figure.5.2.  | Temps de recherche en fonction de la taille du cache                                 | 101 |  |

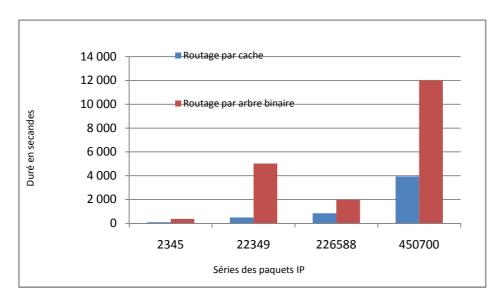

| Figure.5.3.  | Distributions de temps de recherche de route pour les quatre séries                  | 101 |  |

| riguie.3.3.  | de paquets IP                                                                        | 102 |  |

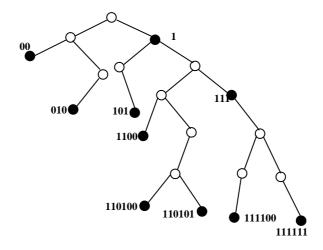

| Figure.5.4.  | Arbre binaire des préfixes construit du Tableau 5.1                                  | 103 |  |

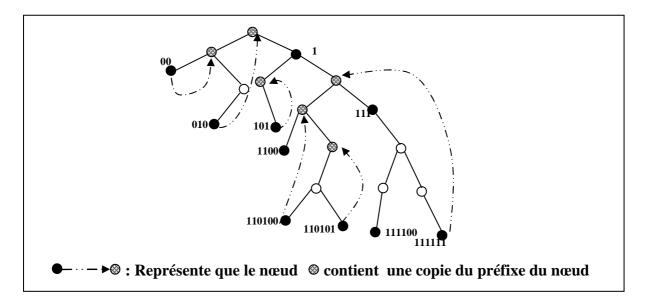

| Figure.5.5.  | L'arbre à contenu dynamique ABCD proposé                                             | 104 |  |

| Figure.5.6.  | Figure 5.6. Structure d'un nœud de l'arbre ABCD                                      |     |  |

| Figure.5.7.  | Figure 5.7. Algorithme de recherche du plus long préfixe pour une adresse IP 1       |     |  |

## Liste des Tableaux

| Tableau.1.1.  | Exemple 1.1 de préfixes.                                                                                                  | 14  |

|---------------|---------------------------------------------------------------------------------------------------------------------------|-----|

| Tableau.2.1.  | Exemple 2.1 de préfixes                                                                                                   | 21  |

| Tableau.2.2.  | Exemple 2.2 de préfixes.                                                                                                  | 22  |

| Tableau.2.3.  | Exemple 2.3 de préfixes                                                                                                   | 25  |

| Tableau.2.4.  | Exemple 2.4 de préfixes                                                                                                   | 27  |

| Tableau.2.5.  | Exemple 2.5 de préfixes                                                                                                   | 29  |

| Tableau.2.6.  | Exemple 2.6 de préfixes [31]                                                                                              | 31  |

| Tableau.2.7.  | Liste des points d'extrémités (en 8-bits) et leurs plus longs préfixes pour les préfixes de l'exemple du tableau.3.6 [31] | 31  |

| Tableau.2.8.  | Exemple 2.7 de préfixes [34]                                                                                              | 33  |

| Tableau.2.9.  | Exemple 2.8 de préfixes.                                                                                                  | 36  |

|               | Comparaison des complexités des différents algorithmes                                                                    | 38  |

| Tableau.2.11. | Exemple 2.9 de préfixes.                                                                                                  | 41  |

| Tableau.3.1.  | Parallélisme de flux                                                                                                      | 51  |

| Tableau.4.1.  | Exemple 4.1 d'une table de routage des préfixes originaux                                                                 | 71  |

| Tableau.4.2.  | Sous table de routage des préfixes expansés de langueur 4                                                                 | 72  |

| Tableau.4.3.  | Intervalles des groupes                                                                                                   | 74  |

| Tableau.4.4.  | Résultats obtenus                                                                                                         | 80  |

| Tableau.4.5.  | Exemple d'une sous-table de routage                                                                                       | 89  |

| Tableaux.4.6. | Exemple des sous-tables de routage                                                                                        | 91  |

|               |                                                                                                                           |     |

| Tableau.5.1.  | Exemple 5.1 d'une Table de routage principale                                                                             | 98  |

| Tableau.5.2.  | Exemple d'une table de routage cache                                                                                      | 99  |

| Tableau.5.3.  | Période de routage en fonction de la taille du cache                                                                      | 103 |

| Tableau.5.4.  | Comparaison de notre algorithme avec l'algorithme de recherche de routes par arbre binaire classique                      | 102 |

| Tableau.5.5.  | Exemple 5.2 d'un e table de routage                                                                                       | 103 |

| Tableau.5.6.  | Performances de l'arbre ABCD                                                                                              | 107 |

| Tableau.5.7.  | Comparaison des performances avec d'autres algorithmes                                                                    | 108 |

## Liste des Abréviations

A

ABCD Arbre Binaire à Contenu Dynamique

ALU Arithmetic and Logical Unit

APC Aligned-Prefix Caching

AS Autonomous System

ASIC Application Specific Integrated Circuits

В

BMP Best Matching Prefix BPT Binary Prefix Tree

$\mathbf{C}$

CAM Content-Addressable Memory

CAO Conception Assistée par Ordinateur

CC-NUMA Cache-Coherent Non-Uniform Memory Access

CIDR Classless Inter-Domain Routing

CM Connexion Machine

CPU Central Processing Unit

D

DA Destination AdressDPT Disjoint Prefix Tree

$\mathbf{E}$

**E-BMP** Equal Best Matching Prefix

$\mathbf{F}$

FAI Fournisseur d'Accès à Internet

FD Flot de DonnéesFE Forwording EngineFI Flot d'Instructions

**FPGA** Field Programmable Gate Array

FTP File Transfer Protocol

G

**G-BMP** Greater **B**est Matching **P**refix

H

HAC Host Address Cache

HDL Hardware Description LanguageHTTP Hyper Text Transfer Protocol

T

IANA Internet Assigned Numbers Authority

**I-BGP** interior **BGP**

ICMP Internet Control Message Protocol

IETF Internet Engineering Task Force

IGMP Internet Group Management Protocol

IP Internet Protocol

IPv4 Internet Protocol Version 4IPV6 Internet Protocol Version 6

IS-IS Intermediate System To Intermediate SystemISO International Organization for Standardization

L

L-BMP Less Best matching PrefixLC-Trie Level Copressed Trie

LPFST Longest Prefix First Search Tree

LSA Link-State Advertisement

M

MAC Media Access ControlMBPT M Binary Prefix TreeME Minimal Expansion

MISD Multiple Instruction stream, Single Data streamMIMD Multiple Instructions stream, Multiple Data stream

MP Mémoire Partagée

MPC Multizone Pipelined Cache

N

**NART** Network Address Routing Table

NCP Network Control Protocol

Nnv Nombre de Nœuds Vide

Np Nombre de préfixe

NPd Nombre de Préfixes Déplacé NTn Nombre Total de Nœuds

0

OSPF Open Shortest Path First

P

PATRICIA Practical Algorithm To Retrieve Information Coded In Alphanumeric

PARIR Parallel Architecture for Routing Information Research

PC-Trie Path Compressed Trie

PRAM Parallel Random Access Machine

PS Port de Sortie

R

RAM Random Access Memory

RFC Request For Comments

RIP Routing Information Protocol

RISC Reduced Instruction Set Computer

RRC Reverse Routing Cache

RTL Resistor-Transistor Logic

S

SIMD Single Instruction stream, Multiple Data stream

CISC Complex Instruction Set Computer

SISD Single Instruction stream, Single Data stream

SMPSymmetric Multi-ProcesseursSMTPSimple Mail Transfer ProtocolSPMDSingle Program Multiple DataSRAMStatic Random Access Memory

$\mathbf{T}$

TCAM Ternary Content-Addressable Memory

TCP Transmission Control Protocol

#### LISTE DES ABREVIATIONS

TTL Time To Live

U

UC Unité de Contrôle

UDP User Datagram Protocol

UR Unité de Recherche)

UT l'Unité de Traitement

$\mathbf{V}$

VHDL Very High Speed Integrated Circuit Hardware Description Language

VLSM Variable-Lenght Subnet Masking

VOIP VOix sur réseau IP

$\mathbf{W}$

WPT Weigted Prefix Tree

## Chapitre 1

## Introduction

Le routeur prend l'adresse IP de destination d'un paquet et cherche dans sa table de routage les informations de routage, cette opération s'appelle consultation d'adresse IP (address lookup). Dans ce contexte, notre travail s'oriente vers l'accélération de cette opération. Dans ce chapitre nous présentons le contexte de travail qui est la recherche d'information de routage dans les routeurs Internet et nous présentons les motivations, les objectifs et les contributions de cette thèse.

#### 1.1. Introduction

Un réseau peut être vu comme un ensemble de ressources mises en place pour offrir un ensemble de services. Dans l'Internet, la communication entre machines est effectuée en utilisant les paquets d'informations. Une fois que les machines émettent leurs paquets dans le réseau, ce sont les routeurs qui retransmettent ces paquets sur les liaisons des réseaux pour les acheminer vers leurs destinations finales. La croissance du nombre d'utilisateurs d'Internet et l'arrivée de nouveaux services et traitements multimédia ont eu comme conséquence l'augmentation des tailles des tables de routages des routeurs et la complexité de l'opération d'acheminement des paquets de données.

Il y a trois facteurs principaux à être considérés dans les réseaux IP pour maintenir un bon service: Liens avec une grande largeur de bande, commutation de données à grande vitesse et taux élevés de l'expédition de paquets.

Actuellement, les liens optiques de transmission de données et la technologie courante de commutation de données permettent la manipulation facile des deux premiers facteurs. Par conséquent, le déploiement des routeurs de rendement élevé pour expédier les paquets IP est la clef au succès des routeurs IP.

Dans l'Internet, chaque paquet est acheminé indépendamment des autres. Ce mode d'opération est connu comme le mode datagramme. Le mode datagramme permet d'offrir un service robuste, car les routeurs peuvent adapter l'acheminement des paquets lors des changements dans la topologie des réseaux. Cependant, le mode datagramme nécessite que les

routeurs aient la capacité suffisante pour traiter tous les paquets arrivant à leurs ports d'entrée. Ainsi, avec l'accroissement du trafic, il est nécessaire d'optimiser la performance des routeurs lors de l'acheminement des paquets.

Chaque routeur maintien une table de routage qui est construite à partir des informations échangées avec d'autres routeurs. Ces échanges d'information sont réalisés par l'intermédiaire de protocoles de routage, tels que RIP, OSPF ou BGP. Cette table de routage contient en général plus d'information que celle strictement nécessaire pour l'acheminement de paquets (comme les informations de gestion du réseau).

Pour acheminer les paquets, les routeurs doivent accomplir deux tâches principales :

Premièrement, les routeurs doivent déterminer où doit envoyer chaque paquet reçu. Plus spécifiquement, les routeurs doivent déterminer, pour chaque paquet reçu, l'adresse du prochain routeur (ou l'adresse de la destination finale s'il s'agit du dernier relais) et le port de sortie par lequel sera réexpédier le paquet. On appelle l'ensemble de ces deux informations les informations de routage. Pour déterminer les informations de routage, le routeur utilise l'adresse IP de destination du paquet reçu pour la recherche dans la table de routage. Cette opération s'appelle consultation d'adresse (*address lookup*) ou recherche d'information de routage.

Deuxièmement, les routeurs doivent commuter le paquet du port d'entrée au port de sortie approprié. Si le lien de sortie est disponible, le paquet sera retransmis sur ce lien ; dans le cas contraire, le routeur doit mémoriser le paquet dans un buffer en attendant que le lien soit disponible.

Dans cette thèse, nous nous focalisons sur la première tâche (décision de routage).

#### 1.2. Protocole IP et adressage

#### 1.2.1. Protocole IP

IP est l'acronyme de "Internet Protocol", il est défini dans la RFC 791 [1] et a été conçu en 1980 pour remplacer NCP (Network Control Protocol) le protocole de l'ARPAnet. Il représente le protocole réseau le plus répandu. Il permet de découper l'information à transmettre en paquets, de les adresser, de les transporter indépendamment les uns des autres et de recomposer le message initial à l'arrivée.

Le protocole IP fait partie de la couche Internet de la suite de protocoles TCP/IP, et permet l'élaboration et le transport des datagrammes IP, sans toutefois en assurer la livraison. Concrètement, le protocole traite les datagrammes IP indépendamment les uns des autres en définissant leur routage et leur expédition utilisant l'adresse IP de destination [1].

#### 1.2.2. Evolution d'adressage IP

#### 1.2.2.1. L'adressage avec classes

Une des tâches fondamentale lors de la mise en place d'un réseau TCP/IP consiste à affecter des adresses Internet aux nœuds du réseau. Ce sont les adresses IP. Si l'affectation des adresses IP peut sembler facile à première vue, il est nécessaire de prendre en considération un certain nombre de points. Pour que l'ensemble soit cohérent et puisse fonctionner, tous les périphériques doivent avoir une adresse unique. De plus, afin de pouvoir communiquer avec les autres nœuds, il est indispensable que ces adresses soient cohérentes entre elles.

La base de l'adressage dans un réseau TCP/IP est l'adresse de la carte réseau (adresse MAC). Elle est inscrite en dur dans le programme implémenté. Pour de nombreuses raisons (changement de carte réseau, facilité de groupage de mêmes types d'adresses), la décision fut prise pour mettre en place un système d'adressage logique indépendant au-dessus des adresses physiques.

#### 1.2.2.1.1. Structure de l'adresse IP

La vision logique de l'Internet créé un réseau virtuel. Chaque connexion de réseau à ce réseau virtuel est identifiée de manière distincte au moyen d'une adresse IP. Les concepteurs de TCP/IP ont choisi un adressage sur 32 bits (IPv4) [2] et 128 bits pour (IPv6). Le réseau virtuel est constitué de réseaux reliés entre eux par le biais de périphériques tels que routeurs ou passerelles.

Afin d'aiguiller les datagrammes IP, les routeurs doivent être en mesure de distinguer différent réseaux logiques. L'adresse IP est structurée de façon à ce qu'elle puisse refléter la distinction entre les différents réseaux logiques. Un certain nombre de bits dans l'adresse IP sont utilisés pour identifier le réseau individuel dans le réseau virtuel, et les bits suivants permettent d'identifier l'hôte au sein du réseau.

| 32 bits |             |

|---------|-------------|

| Netid   | Hostid      |

| N bits  | 32 – N bits |

La méthode consistant à partager l'adresse IP entre un numéro de réseau et un numéro d'hôte constitue un plan d'adressage hiérarchique, ce qui permet de rendre le routage beaucoup plus efficace. La fonction première d'un routeur est d'envoyer un datagramme IP dans au réseau. A cet effet, les routeurs doivent stocker les informations concernant les NetIds et non les HostIds.

Le nombre de Netids est forcément inférieur aux Hostids, ce qui maintient à un nombre raisonnable la quantité d'informations qu'un routeur doit connaître. Si l'on n'avait pas établit cette distinction entre Netid et Hostid (en choisissant un système d'adressage plat, plutôt qu'un plan d'adressage hiérarchique), les routeurs auraient dû stocker les quarte milliards d'adresses IP.

A partir du nombre de 32 bits utilisé pour l'adresse IPv4 [2], les concepteurs ont décidé que l'on utiliserait le premier, les 2 premiers ou les 3 premiers octets comme Netid selon les classes d'adresses IP.

#### 1.2.2.1.2. Classes d'adresses IP

Dans les premières années d'Internet, l'assignation des adresses aux réseaux finaux consistait à octroyer le premier octet de l'adresse au réseau, c'est-à-dire que 256 réseaux de 16 millions d'adresses étaient possibles. Devant la limitation qu'impose ce modèle, une modification de la façon dont les adresses sont assignées est indispensable. En 1981, la RFC 790 [3] (*Assigned numbers*) prévoit qu'une adresse IP est divisée en deux parties : une partie servant à identifier le réseau (net id) et une partie servant à identifier un poste sur ce réseau (host id).

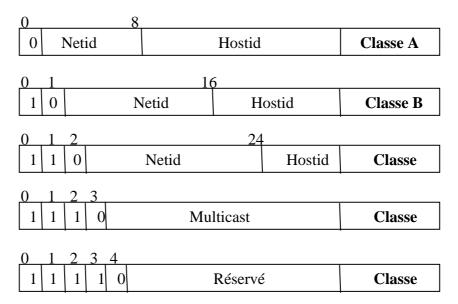

Il existe 5 classes d'adresses IP. Chaque classe est identifiée par une lettre allant de A à E. Ces différentes classes ont chacune leurs spécificités en termes de répartition du nombre d'octet servant à identifier le réseau ou les ordinateurs connectés à ce réseau :

- Une adresse IP de classe A dispose d'une partie *NetId* comportant uniquement un seul octet.

- Une adresse IP de classe B dispose d'une partie *NetId* comportant deux octets.

- Une adresse IP de classe C dispose d'une partie *NetId* comportant trois octets.

- Les adresses IP de classes D et E correspondent à des adresses IP particulières.

Afin d'identifier à quelle classe appartient une adresse IP, il faut examiner les premiers bits de l'adresse.

Figure.1.1. Classes d'adresses IP

#### Pourquoi utiliser des classes d'adresses spécifiques ?

Les différents types de classes d'adresses IP sont définis pour répondre aux besoins des réseaux de différentes tailles. Sur demande, l'autorité d'enregistrement du réseau affecte un numéro de réseau (NetId) à une organisation. Une fois ce numéro alloué à une organisation, il incombe à cette dernière d'affecter les numéros d'hôte (HostId).

#### 1.2.2.1.3. Adresses IPv4

Ces adresses 32 bits correspondent au format d'adressage IP initialement conçu pour TCP/IP. À l'origine, les réseaux IP se décomposent en trois classes, A, B et C. Le numéro de réseau attribué à un réseau reflète cette identification de classe, tandis que les 8 bits ou plus supplémentaires représentent un hôte. Les adresses IPv4 basées sur les classes requièrent la configuration d'un masque de réseau pour le numéro de réseau. En outre, ces adresses étaient souvent divisées en sous-réseaux afin d'augmenter le nombre d'adresses disponibles pour les systèmes du réseau local.

Aujourd'hui, les adresses IP sont appelées adresses IPv4 ou IPv6. Il est désormais impossible d'obtenir des numéros de réseau IPv4 basés sur les classes auprès d'un fournisseur de services Internet, mais de nombreux réseaux les utilisent encore.

#### Limites d'IPv4

La version IPv4 a été en service pendant presque trois décennies. Mais, elle commence à montrer des limites vis-à-vis des demandes émergentes en termes de la cardinalité d'espace d'adressage, la mobilité à haute densité, le multimédia, et la forte sécurité. Par conséquent, l'IPv6 crée un nouveau format d'adresse IP, de sorte que le nombre d'adresse IP ne s'épuise pas pendant plusieurs décennies, ou bien aussi longtemps que possible à ce qu'une nouvelle récolte entière d'équipements soit reliée à l'Internet. IPv6 améliore également le routage et la configuration automatique de réseau.

#### 1.2.2.1.4. Adresses IPv6

IPv6 est le protocole actuel d'Internet, qui était d'abord appelé IPng (Internet Next Generation). L'IETF [4] a développé les caractéristiques de base de ce protocole pendant les années 90 pour supporter la migration à un nouvel environnement. IPv6 défini dans RFC 2460 [5] et RFC 3513 [6] est considéré comme étant une version améliorée d'IP. Celui-ci est conçu pour coexister avec IPv4 et pour fournir par la suite de meilleures possibilités d'interconnexion de réseaux qu'avec IPv4 [2].

L'IETF a déployé des adresses IPv6 128 bits afin de résoudre à long terme le problème d'épuisement des adresses IPv4 disponibles. Les adresses IPv6 assurent un espace d'adressage plus étendu qu'IPv4 [7]. De même que les adresses IPv4 au format CIDR, les adresses IPv6 ne possèdent aucune notion de classe de réseau ni de masque de réseau. Comme dans CIDR, les adresses IPv6 utilisent des préfixes pour désigner la partie de l'adresse définissant le réseau du site.

Les avantages d'IPv6 peuvent être résumés comme suit :

- Facteur d'échelle (scalabilité) : les adresses IPv6 sont représentées sur 128 bits par contre celles d'IPv4 sont représentées sur 32 bits.

- **Sécurité** : IPv6 inclut la sécurité dans ses spécifications, tels que le chiffrement de données et l'authentification de la source de données.

- Application en temps réel : Pour fournir un meilleur support pour le trafic en temps réel (par exemple, VoIP), IPv6 inclut "des flux étiquetés" dans ses spécifications. Grâce à ce mécanisme, les routeurs peuvent identifier le flux de bout en bout auquel appartiennent les paquets transmis.

- Adressage et routage : IPv6 améliore l'adressage et le routage hiérarchique.

- Extensibilité : IPv6 a été conçu pour être extensible et offre un support pour de nouvelles options.

#### 1.2.2.1.5. Sous-réseaux

Les formats d'adresses IPv4 ont étés conçus pour s'adapter à des réseaux de différentes tailles. Ces formats convenaient bien dans les premiers temps de l'internet. La principale faiblesse du format IPv4 réside dans le gâchis d'espace d'adressage consécutif à la conception d'un inter réseau.

Pour pallier à ce défaut, la RFC 950 [1] a défini et normalisé le concept de sousréseau en 1985. Les sous-réseaux permettent d'utiliser un numéro de réseau unique pour construire plusieurs réseaux interconnectés. Le préfixe de numéro de réseau est partagé entre plusieurs réseaux appelés sous-réseaux. Cette mise en sous-réseaux est généralement utilisée lorsque le même numéro de réseau est utilisé pour plusieurs réseaux interconnectés.

#### Masque de sous-réseau

Outre l'adresse IP, une machine doit aussi connaître le nombre de bits attribués à l'identification du sous-réseau et à l'identificateur de machine. Ces informations sont fournies par le masque de sous-réseau (Netmask). Ce masque est un masque de 32 bits (pour IPv4) contenant soit des bits à 1 pour l'identification du réseau et des bits à 0 pour l'identification de machines.

#### 1.2.2.2. Structuration des adresses et agrégation

Un des problèmes majeurs dans le routage est la croissance incontrôlée des tables de routage. Ce phénomène est dû à une mauvaise agrégation des adresses dans les tables. Il faudrait être capable de router des ensembles de réseaux identifiés par un seul descripteur. CIDR apporte une amélioration.

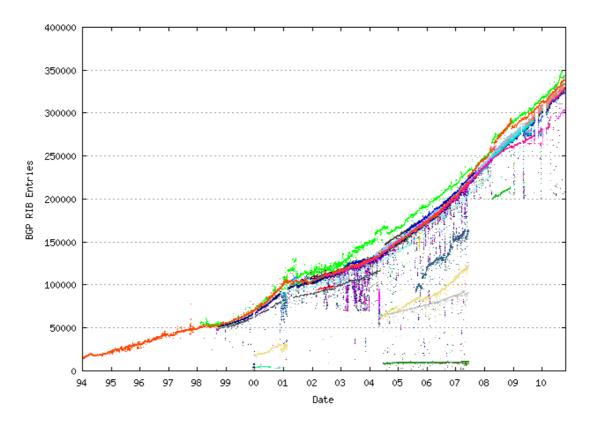

#### 1.2.2.2.1. Evolution des tailles des tables de routage

Actuellement, pour pouvoir assurer une bonne agrégation, les règles utilisées par CIDR [8] pour IPv4 sont conservées, mais la gestion des tables de routage dans le cœur du réseau s'en trouvera quand même améliorée car :

- Dès le début, le plan d'adressage est hiérarchique et éliminant les longs préfixes,

- Les sites multi-domiciliés posséderont autant d'adresses que de fournisseurs, permettant ainsi de garantir une agrégation.

- Des mécanismes de renumérotation automatiques permettent aux sites de changer facilement de préfixe quand cela est nécessaire.

La figure suivante présente l'évolution des tables de routage dans le cœur de l'Internet.

Figure.1.2. Evolution des tailles des tables de routage [8]

#### 1.2.2.2.2. CIDR (Classless Inter-Domain Routing)

En 1992, la RFC 1338 [9] (Supernetting: an Address Assignment and Aggregation Strategy) propose de détruire la notion de classe qui n'était plus adaptée à la taille d'Internet. Le CIDR (Classless Inter-Domain Routing) [10], [8] est mis au point en 1993, afin de diminuer la taille de la table de routage contenue dans les routeurs. Ce but est atteint en agrégeant plusieurs entrées de cette table en une seule.

Le but était de pouvoir regrouper plusieurs réseaux de classe C dans un seul bloc d'adresses de 2<sup>n</sup> x 256 afin de poser une seule entrée vers ces réseaux (agrégation de routes), on parlait alors de supernetting, ceci fut ensuite propagé aux adresses de classe B bien que le besoin d'agrégation y soit moindre, puis enfin aux réseaux de classe A, bien que le problème d'agrégation des routes ne s'y pose pas.

En fait c'est toute la représentation de l'espace d'adressage qui a été changé.

#### **Principe**

La conception initiale de sous-réseaux par classe nécessitait que tous les sous-réseaux d'un même réseau classé soient de la même taille. Cela découlait du fait que les routeurs n'incluaient pas de données de masque de sous-réseau dans leurs mises à jour de routage. Un routeur programmé avec une adresse et un masque de réseau sur une interface appliquait automatiquement le même masque aux autres sous-réseaux dans sa table de routage. Du fait de cette limite, le schéma d'adressage IP nécessitait la planification de masques de sous-réseau de longueur fixe.

Cependant, les masques de sous-réseau de longueur fixe peuvent gaspiller un nombre important d'adresses IP. Par exemple, prenons une organisation comprenant un site doté d'environ 8 000 hôtes et trois autres emplacements dotés respectivement de 1 000, 400 et 100 hôtes. Avec un masque de sous-réseau de longueur fixe, chaque sous-réseau devrait prendre en charge au moins 8 000 hôtes, y compris le sous-réseau affecté à l'emplacement qui ne nécessite que 100 adresses.

Le masquage de sous-réseau de longueur variable (VLSM) permet de résoudre ce problème. L'adressage VLSM permet de diviser un espace d'adressage en réseaux de tailles différentes. Cette opération s'effectue en découpant les sous-réseaux. Pour ce faire, les routeurs doivent recevoir des informations de routage incluant l'adresse IP du réseau, ainsi que des données de masque de sous-réseau indiquant le nombre de bits qui composent la partie réseau de l'adresse IP. Le masquage de sous-réseau de longueur variable permet d'économiser des milliers d'adresses IP que la création traditionnelle de sous-réseaux par classe aurait gaspillée.

En plus du masquage de sous-réseau de longueur variable (VLSM), le document RFC1519 [11] a proposé le routage inter-domaine sans classe CIDR (*Classless Inter-Domain Routing*), lequel a été accepté. Le routage inter-domaine sans classe (CIDR) ignore les classes de réseau basées sur la valeur des bits d'ordre haut. Il identifie les réseaux uniquement d'après le nombre de bits du préfixe réseau, lequel correspond au nombre de 1 dans le masque de sous-réseau.

L'adresse 172.16.1.1/16 est un exemple d'adresse IP écrite à l'aide de la notation CIDR dans laquelle /16 représente le nombre de bits du préfixe réseau.

Les protocoles CIDR ont donné aux routeurs la capacité de déterminer le préfixe réseau sans être limités aux bits d'ordre haut. La suppression de cette restriction a éliminé la nécessité d'attribuer les adresses IP enregistrées par classes d'adresses.

Avant l'utilisation du protocole CIDR, un FAI nécessitant 3 000 adresses d'hôte pouvait demander soit un espace d'adressage de classe B complet, soit plusieurs adresses réseau de classe C pour répondre à ses besoins. Avec un espace d'adressage de classe B, le FAI aurait gaspillé des milliers d'adresses enregistrées. Avec plusieurs adresses de classe C, il pouvait être difficile de concevoir le réseau FAI de sorte qu'aucune section unique ne nécessite plus de 254 adresses d'hôte. Les tables de routage contenant de nombreuses adresses de classe C peuvent également devenir trop volumineuses et difficiles à gérer.

Du fait qu'il ignore les classes d'adresses traditionnelles, le protocole CIDR permet au FAI de demander un bloc d'adresses qui soit fonction du nombre d'adresses d'hôte requis. Les super-réseaux, créés en regroupant un groupe d'adresses de classe C dans un bloc de grande taille, permettent une attribution plus efficace des adresses. Un exemple de super-réseau pourrait être 192.168.0.0/19. L'utilisation des 19 premiers bits de l'adresse IP pour le préfix réseau permet à ce super-réseau de contenir 8190 adresses d'hôte possibles. Un FAI peut utiliser un super-réseau comme un grand réseau unique ou le diviser en autant de réseaux plus petits que nécessaire pour répondre à ses besoins.

Dans cet exemple de super-réseau, l'adresse de classe C privée 192.168.0.0 est utilisée. En réalité, la plupart des réseaux utilisant l'adressage privé utilisent des adresses réservées et le découpage en sous-réseaux de classe A ou B. Bien que l'adressage classé et le masquage de sous-réseau de longueur fixe deviennent moins courants, il est important de comprendre le fonctionnement des méthodes d'adressage. De nombreux périphériques utilisent encore le masque de sous-réseau par défaut si aucun masque de sous-réseau personnalisé n'est défini.

#### Communications entre sous-réseaux

Lorsqu'un réseau est divisé en sous-réseaux, chacun de ces sous-réseaux constitue réellement un réseau à part entière. Les routeurs ayant pour fonction de connecter les réseaux, un routeur est donc indispensable pour qu'un périphérique d'un sous-réseau puisse communiquer avec un périphérique d'un autre sous-réseau.

Pour déterminer le nombre d'hôtes requis dans chaque sous-réseau, il est nécessaire d'inclure l'interface de routeur, ou l'interface de passerelle, ainsi que les périphériques hôte individuels.

Chaque interface de routeur doit avoir une adresse IP dans le même sous-réseau que le réseau d'hôtes qui lui est lié.

#### Adresses IPv4 au format CIDR

L'IETF [4] a développé des adresses CIDR (Classless Inter-Domain Routing), routage inter-domaine sans classe, dans le but de résoudre à court ou moyen terme le problème d'épuisement des adresses IPv4 [2]. Par ailleurs, le format CIDR a été conçu pour remédier au manque de capacité des tables de routage Internet. Une adresse IPv4 avec notation CIDR présente une longueur de 32 bits et le même format décimal avec points. Cependant, CIDR

ajoute une désignation de préfixe juste après l'octet le plus à droite afin de définir la portion de réseau de l'adresse IPv4.

#### 1.3. Recherche d'information de routage dans un routeur IP

#### 1.3.1. Routeurs IP

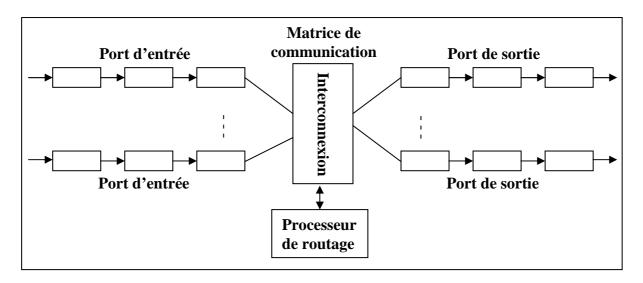

Les routeurs sont les dispositifs permettant de "choisir" le chemin que les datagrammes vont emprunter pour arriver à la destination. Il s'agit de machines ayant plusieurs ports d'entrée dont chacun est relié à un réseau différent. Ainsi, dans la configuration la plus simple, le routeur n'a qu'à "regarder" sur quel réseau se trouve un ordinateur pour lui faire parvenir les datagrammes en provenance de l'expéditeur.

Toutefois, sur Internet le schéma est beaucoup plus compliqué pour les raisons suivantes:

- Le nombre de réseau auxquels un routeur est connecté est généralement important.

- Les réseaux auxquels le routeur est relié peuvent être reliés à d'autres réseaux que le routeur ne connaît pas directement.

Ainsi, les routeurs fonctionnent grâce à des tables de routage et des protocoles de routage, selon le modèle suivant:

- Le routeur reçoit une trame provenant d'une machine connectée à un des réseaux auquel il est rattaché.

- Le routeur regarde l'entête du datagramme, si l'adresse IP de destination appartient à l'un des réseaux auxquels une des interfaces du routeur est rattaché, l'information doit être envoyée à la couche supérieure après que l'entête IP ait été désencapsulée (enlevée), dans ce cas on parle de remise directe.

- Si l'adresse IP de destination fait partie d'un réseau différent, le routeur consulte sa table de routage, une table qui définit le chemin à emprunter pour une adresse donnée, le routeur envoie le datagramme grâce au port de sortie relié au réseau sur lequel le routeur décide d'envoyer le paquet, on parle de remise indirecte.

Figure.1.3. Architecture d'un routeur Internet

#### 1.3.2. Table de routage

La table de routage est une table de correspondance entre l'adresse de la machine ou le préfixe du sou-réseau visée et le nœud suivant auquel le routeur doit délivrer le message, elle peut être entrée manuellement par l'administrateur (*routage statique*) ou construite par le routeur en fonctions des informations qu'il reçoit (*routage dynamique*). En réalité il n'est pas nécessaire de stocker l'adresse IP complète de la machine: Seul l'identificateur du réseau de l'adresse IP est stocké.

La table de routage est donc un tableau contenant des paires d'adresses:

| Adresse de destination | Adresse du prochain routeur directement accessible | Interface |  |

|------------------------|----------------------------------------------------|-----------|--|

|------------------------|----------------------------------------------------|-----------|--|

Ainsi grâce à cette table, le routeur, connaissant l'adresse du destinataire encapsulé dans le message, va être capable de savoir sur quelle interface envoyer le message (cela revient à savoir quelle carte réseau utiliser), et à quel routeur, directement accessible sur le réseau auquel cette carte est connectée, remettre le datagramme.

Ce mécanisme consistant à ne connaître que l'adresse du prochain maillon menant à la destination est appelé routage par sauts successifs (*next-hop routing*).

Le message est ainsi remis de routeur en routeur par sauts successifs, jusqu'à ce que le destinataire appartienne à un réseau directement connecté à un routeur. Celui-ci remet alors directement le message à la machine visée.

Dans les premiers grands réseaux, les tables de routage étaient statiques et donc maintenues à jour par des techniciens de bout en bout. De nos jours, les mises à jour des tables de routage et le calcul du meilleur chemin sont automatiquement propagés sur le réseau par les protocoles de routage.

#### 1.3.3. Consultation d'adresses IP (Notre contribution)

Pour acheminer les paquets, les routeurs doivent déterminer où doit envoyer chaque paquet reçu. Plus spécifiquement, les routeurs doivent déterminer, pour chaque paquet reçu, l'adresse du prochain routeur (ou l'adresse de la destination finale s'il s'agit du dernière relais) et le port de sortie par lequel sera réexpédié le paquet. On appelle l'ensemble de ces deux informations l'information de routage.

Pour déterminer l'information de routage, le routeur consulte l'adresse de destination du paquet reçu dans une table de routage. Cette opération s'appelle consultation d'adresse (address lookup).

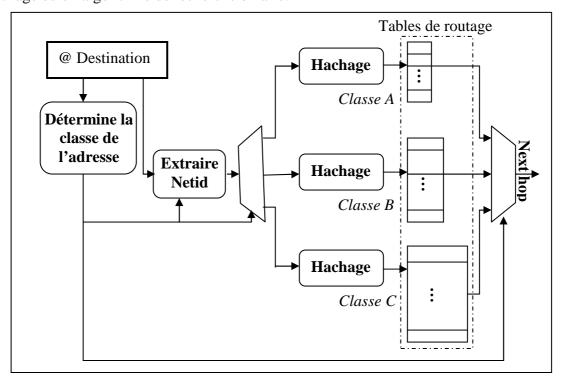

#### 1.3.3.1. Consultation d'adresses IP dans le cas d'adressage en classes

L'architecture d'adressage en classe basée sur des routeurs permet d'utiliser une opération de recherche relativement simple. En générale, la table de routage avait trois parties, une pour chacune des trois classes unicast A, B et C. Les entrées de la table de routage sont des tuples de la forme « *Netid*, adresse de *Next-hop* ». Toutes les entrées de la même partie *Netid* sont de largeur fixe : 7, 14 et 21bits respectivement pour les classes A, B et C, et l'opération de recherche pour chaque paquet entrant a procédé comme dans la figure.1.4. Tout d'abord, la classe a été déterminée à partir des bits les plus significatifs de l'adresse de destination du paquet. Ceci à son tour de déterminer lequel des trois parties de la table de routage à utiliser, en suite le routeur effectuer une recherche pour une correspondance exacte entre le *Netid* du paquet entrant et une entrée dans la partie sélectionnée de la table de routage.

La recherche avec correspondance exacte peut être effectuée en utilisant, par exemple, le hachage ou un algorithme de recherche binaire.

Figure.1.4. Implémentation de l'opération de lookup dans le cas d'adressage en classes

L'dressage en classes a bien fonctionné dans les premiers jours de l'Internet mais, à cause de la croissance d'Internet, deux problèmes ont survenu : Une insuffisance de l'espace d'adressage IP et une croissance exponentielle des tailles des tables de routage ce qui complique l'opération de recherche dans ces tables de routage.

Le problème de tailles des tables de routages est dû au fait que le routeur IP doit stocker toutes les adresses *Netid* dans sa table de routage. En conséquence, les tables de routage sont en croissance exponentielle. Ceci a placé une charge élevée sur les ressources du processeur et la mémoire des routeurs de l'Internet.

Dans une tentative pour ralentir la croissance des tailles des tables de routage et de permettre une utilisation plus efficace de l'espace d'adressage IP, un nouveau schéma d'adressage et de routage appelé CIDR (*Classless Inter-Domain Routing*) a été adopté en 1993 [11] [10].

#### 1.3.3.2. Consultation d'adresses IP dans le cas d'adressage sans-classes (CIDR)

Pour pouvoir passer à l'échelle, les tables de routage n'ont pas une entrée pour chaque adresse destination, mais une entrée par groupes d'adresses. En particulier, les adresses sont agrégées en utilisant leurs préfixes communs. Ainsi, chaque entrée de la table de routage contient l'information de routage correspondant à un groupe d'adresses destination représenté par le préfixe commun de ces adresses. Historiquement, il y avait trois tailles fixes de préfixes (8, 16 et 24 bits). Chaque taille fixe de préfixe déterminait une classe différente d'adresses. Mais à l'heure actuelle, la taille des préfixes peut être de 0 à 32 bits pour le protocole IPv4 et de 0 à 128 bits pour IPv6 dans ce que l'on appelle le routage inter domaines sans classes (CIDR).

Une des opérations essentielles pour acheminer les paquets arrivant à un routeur est la décision de routage, c'est-à-dire la recherche d'information de routage dans la table de routage (plus long préfixe correspondant). Depuis l'introduction de CIDR (*Classless Interdomain Routing*), cette recherche d'information de routage consiste à trouver l'entrée de la table de routage ayant le plus long préfixe commun avec l'adresse destination du paquet à acheminer. En effet, plusieurs entrées de la table de routage peuvent avoir un préfixe commun avec l'adresse destination, mais l'entrée avec le plus long préfixe aura l'information de routage la plus spécifique et donc c'est cette entrée qui doit être utilisée pour effectuer l'acheminement du paquet.

Avec CIDR, La table de routage d'un routeur se compose d'entrées de la forme « préfixe, Next-Hop », où le préfixe est un préfixe IP et Next-Hop est l'adresse IP du prochain saut. Une adresse IP de destination correspond à un préfixe si les bits significatifs du préfixe sont identiques aux premiers bits de l'adresse IP de destination. L'opération de recherche d'information de routage pour un paquet entrant exige de trouver le préfixe le plus spécifique pour le paquet. Cela implique que le routeur a besoin de résoudre le problème de plus long préfixe correspondant à l'dresse IP du paquet (longest prefix matching problem), défini comme suit :

**Définition.1.1:** Le problème de recherche du plus long préfixe correspondant à une adresse IP est le problème de recherche de l'entrée de la table de routage contenant le plus long préfixe parmi tous les préfixes (dans d'autres entrées de la table de routage) correspondant l'adresse de destination du paquet entrant. Ce plus long préfixe est appelé le plus long préfixe correspondant (*longest prefix matching*).

**Exemple.1.1:** Prenant comme exemple un routeur contenant une table de routage représentée dans le tableau.1.1. Si un paquet entrant à ce routeur a une adresse de destination « 200.11.0.1 », elle corresponde les deux préfixes 200.11.0.0/22 et 200.11.1.1/20 mais le préfixe 200.11.0.0/22 est plus long que le préfixe 200.11.1.1/20, alors le paquet sera transmis à l'interface de sortie Nh<sub>2</sub> du routeur.

| Préfixe       | Next-Hop |

|---------------|----------|

| 192.2.0.0/22  | Nh1      |

| 200.11.0.0/22 | Nh2      |

| 192.2.2.0/24  | Nh3      |

| 200.11.1.1/20 | Nh4      |

| 192.2.3.0 /18 | Nh4      |

| 200.10.0.0/16 | Nh1      |

| 192.1.1.0/10  | Nh2      |

| 200.3.2.0/18  | Nh3      |

Tableau.1.1. Exemple 1.1 de préfixes

#### 1.4. Difficulté de recherche d'information de routage

Afin d'augmenter l'efficacité du routage dans l'Internet, plusieurs adresses destination sont agrégées en une seule entrée dans une table de routage. Au départ, cette agrégation correspondait au regroupement de toutes les adresses appartenant à un même réseau. En conséquence le routage était effectué en considérant uniquement les réseaux et non pas chaque hôte en particulier. En raison de la façon dont les adresses sont allouées, toutes les adresses appartenant à un même réseau ont le même préfixe. La recherche dans la table de routage peut s'effectuer en comparant les préfixes avec les bits correspondants de l'adresse IP de destination. Avec cette agrégation d'adresses, la taille des tables de routage n'augmente pas avec le nombre de hôtes, cependant le nombre d'entrées dans la table augmente toujours avec le nombre de réseaux.

Depuis l'apparition du système d'adressage CIDR [10], [8] les difficultés d'expédition des paquets IP sont à cause de :

- Les longueurs du préfixes sont variables et l'adresse du paquet de données ne donne pas une information sur la longueur du préfixe à consulter;

- Une adresse IP peut correspondre à plusieurs préfixes dans la table de routage et le plus long préfixe correspondant devrait être choisi.

L'adresse IP de destination d'un paquet de données ne contient pas les informations nécessaires pour déterminer la longueur du préfixe à consulter (le plus long préfixe correspondant cette adresse). Par conséquent, nous ne pouvons pas trouver la correspondance en utilisant un algorithme de recherche de correspondance exacte (par exemple, en utilisant le hachage ou bien une procédure de recherche binaire). Au lieu de cela, une recherche du plus long préfixe correspondant doit déterminer à la fois la longueur du plus long préfixe correspondant ainsi que l'entrée de la table de routage contenant le préfixe de cette longueur qui correspond l'adresse de destination du paquet entrant.

#### 1.5. Contributions

Cette thèse a pour but l'étude du problème de recherche d'information de routage au niveau des tables de routage des routeurs Internet.

Les contributions de nos recherches sont multiples :

- L'étude bibliographique approfondie (chapitre 2) nous a permis de : Synthétiser les concepts relatifs aux tâches des routeurs IP, et de dégager la problématique sur laquelle nous avons travaillé, et de faire une classification des solutions proposées pour notre problématique qui est la recherche d'information de routage au niveau d'une table de routage d'un routeur IP, vue la croissance exponentielle des tailles des tables de routage.

- Proposition des solutions pour notre problématique (Chapitre 4 et 5). Compte tenu que le but principal d'un routeur est d'acheminer des paquets, un facteur capital dans la performance d'un routeur est la vitesse avec laquelle le routeur trouve les informations de routage. Une façon d'optimiser le temps pour trouver le plus long préfixe, et donc de trouver l'information de routage, et d'utiliser un mécanisme efficace de recherche du plus long préfixe. Dans cette thèse nous proposons des mécanismes de recherche du plus long préfixe correspondant à une adresse IP dans une table de routage, les mécanismes que nous avons proposés dans cette thèse contribuent à améliorer la performance de l'acheminement de paquets dans les routeurs IP.

Pour les solutions proposées, la démarche suivie est :

#### Proposition d'une solution matérielle :

Algorithme et architecture parallèle dédiée. Nous proposons une architecture parallèle appelée « PARIR » (*Parallel Architecture for Routing Information Research*) et ce pour la recherche d'information de routage (*Next-hop*) ou bien le port de sortie pour un paquet de données. À la différence d'autres approches notre mécanisme basé sur le critère de longueur

des préfixes pour regrouper les préfixes dans des sous tables de routages équilibrés et manipulés en parallèle par une architecture parallèle dédiée afin d'accélérer l'opération de recherche du plus long préfixe pour une adresse IP d'un paquet de données reçue d'un routeur.

Une modélisation et description VHDL de cette architecture nous permettent de tester par simulation les différents modules de notre architecture.

#### **Proposition d'une solution logicielle :**

Elle consiste en un algorithme avec table de routage cache. Nous proposons une technique de recherche d'information de routage basée sur une table de routage cache qui mémorise les adresses IP récemment consultées et leurs informations de routage pour augmenter la vitesse de recherche d'information de routage dans un routeur IP, le routeur extraira l'adresse IP de destination d'un paquet de données et cherche l'interface de sortie correspondante dans la table de routage cache, Si cette information n'existe pas dans la table de routage cache une nouvelle recherche est déclenchée dans la table de routage principale utilisant la technique classique de recherche par préfixes.

#### Proposition d'une autre solution logicielle :

Elle consiste en un algorithme avec arbre binaire à contenu dynamique. Un nouvel algorithme de recherche de plus long préfixe en utilisant un arbre binaire à contenu dynamique (ABCD) est proposé. Le contenu de cet arbre est variable selon les adresses IP traitées par le routeur. La technique proposée sert à exploiter les nœuds vides de l'arbre binaire de préfixes [12] par le placement des copies de préfixes les plus récemment utilisés dans les nœuds vides des niveaux supérieurs de l'arbre, de tel sorte que l'opération de recherche du plus long préfixe se termine dès que le plus long préfixe correspondant à l'adresse IP du paquet de données est trouvée dans un certain nœud interne dans l'arbre binaire sans arriver obligatoirement à une feuille.

#### Étude de performance :

Des modèles de simulation sont développés pour les tests de nos solutions proposées. Plusieurs scénarios et paramètres de simulation sont considérés. Les paramètres utilisés reflètent exactement les caractéristiques du problème de recherche de plus long préfixe dans une table de routage. Les résultats sont analysés en se basant sur une étude comparative par rapport aux autres propositions.

Ces différentes propositions ont été validées par la communauté scientifique et ont donné lieu à deux publications dans des revues internationales et à six communications dans des conférences internationales.

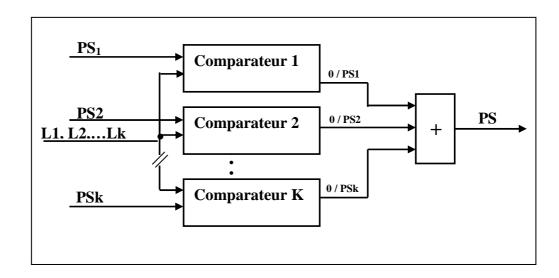

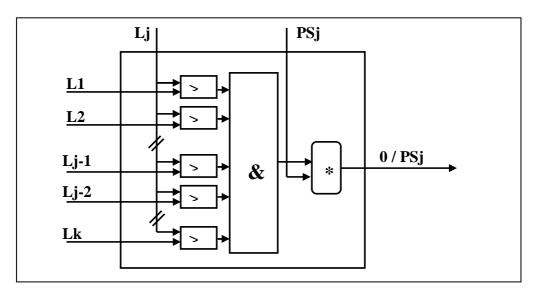

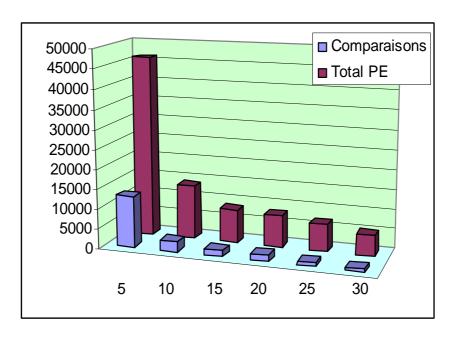

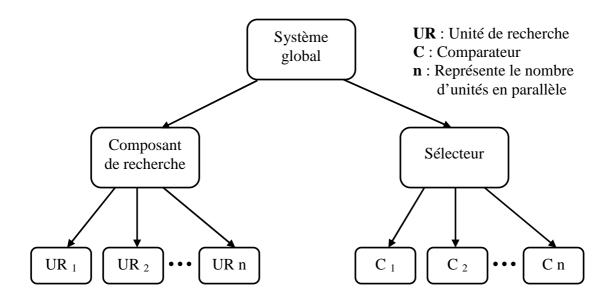

#### 1.6. Plan de la thèse